# electro. Ectemica

**C**85.00

# PREMIO AEP 1974: Mención Especial

# INTERFASE Y CONTROLADOR PARA UN SISTEMA DE DESPLIEGUE VISUAL (Display X-Y)

Dr. Ronald Woodman Ing. César González

#### **PROLOGO**

Como resultado de un Proyecto elaborado en el Radio Observatorio de Jicamarca (ROJ) se tiene el presente escrito.

El ROJ dispone de un Centro de Cómputos alrededor del cual, paulatina y sistemáticamente se están enlazando otros Sistemas a modo de Unidades Periféricas. Gran parte del diseño se realiza aquí complementándose con equipo comercial.

El diseño del Controlador para una Unidad de éstas es tema de este

#### Introducción

La Fig. 1 muestra una foto del Sistema de Computación DC6024/3 instalado en el ROJ. Como parte de éste y ya en funcionamiento está el Sistema de Despliegue Visual (XY Display).

La función de este último, es la de permitir visualizar en forma análoga y a través de un tubo de rayos catódicos (CRT) datos que como es de suponer, lo están en forma digital en la Computadora. También permite el uso de la señal análoga obtenida en otros fines aparte del de visualización.

Aunque en la redacción se intenta ser claro y presentar ideas básicas que permitan seguir la lectura sin dificultades, puede ser necesario un mínimo de conocimiento sobre Sistemas Digitales y de Computación para una comprensión cabal del contenido. En tal sentido es recomendable la lectura previa de las Referencias Bibliográficas presentadas al final del Informe cuando la situación así lo permita.

Igualmente, se sugiere leer el Apéndice A para conocer y entender la nomenclatura usada en los diagramas aquí presentados.

Gran parte de este trabajo, tiene que estar de acuerdo con especificaciones de la Datacraft Corporation fabricantes de la DC6024/3, por este motivo es ineludible la utilización de términos en Inglés que en la mayoría de casos se convierten en abreviaciones. Esto debe justificar la inclusión de palabras no españolas y también el Apéndice B que es un Indice de abreviaturas.

En el Capítulo 1 se dan más detalles de la DC6024/3, incluyendo el Software disponible. El Capítulo 2 introduce el importante tema de la entrada y salida de datos, comandos y sensados (status) y concluye con un resumen (2-6), el cual sería conveniente se lea también al iniciarse este capítulo. El Capítulo 3 contiene diagramas y explicación de los Circuitos Implementados en el ROJ, Tablas, Montaje, en fín, la parte práctica del trabajo. El Capítulo 4 muestra ejemplos de los múltiples usos que podrían darse a este dispositivo.

Cierto es que existen sofisticados equipos comerciales que cumplen con los propósitos alcanzados por el presente diseño y mucho más, pero también lo es, que muchas veces estos equipos sobrepasan las necesidades reales y su costo resulta prohibitivo. El diseño, tema de este proyecto ha sido realizado y elaborado totalmente en el ROJ, utilizando materiales de los que allí se disponen y con un costo estimado comparativamente bajo. Otra ventaja, es que se usa un osciloscopio como pantalla, herramienta útil y bastante común. Con algunas modificaciones bien podría adaptarse este diseño a otros pequeños Centros de Cómputo.

#### 1 SISTEMA DE COMPUTACION DE 6024/3

#### 1-1 Descripción Básica del Sistema de Computación

La Datacraft 6024/3 es una computadora digital de propósitos generales, mediana escala, con un tiempo de reloj de l $\mu$ seg. utiliza una palabra de 24 bits más un bit de paridad y control de tiempo real asemejándose a un multiprocesador o a un Sistema de gran escala por

estas y otras características. Se incluye un apéndice al final más detallado sobre la DC6024/3.

Se dispone de varias unidades periféricas en las instalaciones de Jicamarca, entre las cuales están los equipos de cinta magnética, lectora de tarjetas, teletipo, conversor analógico digital (ADC), conversor digital-analógico (DAC) tema de este trabajo, y un Controlador de Radar en las últimas etapas de prueba y de instalación. La interfase de la unidad central de procesamiento (CPU) con dichos equipos es más o menos estandard a través de canales, los cuales pueden utilizar un sistema de prioridades y de interrupción conveniente o a través de un canal con control automático de bloques (ABC) para la transmisión de datos en bloques y en forma automática como el nombre bien lo sugiere. Más adelante se tratará en más detalle estos puntos que ahora han sido incluidos a modo de referencia.

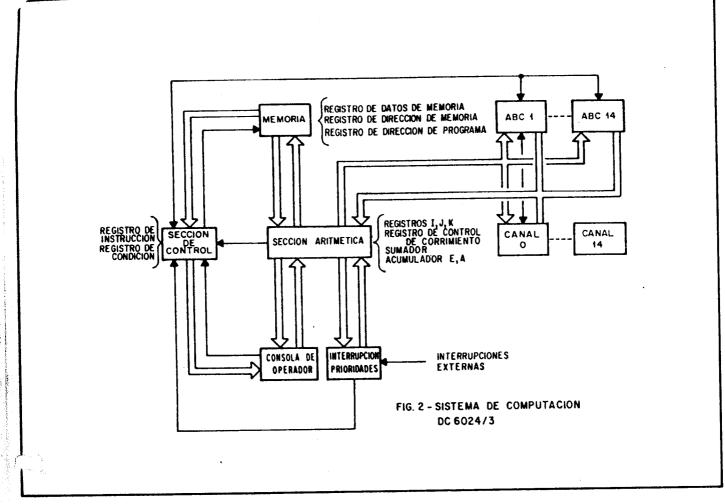

Como cualquier computadora digital, podemos distinguir en la Unidad Central de Procesamiento diferentes secciones, tales como la Aritmética, de Control, de Memoria, etc. Un diagrama de bloques de la Computadora aparece en la Fig. 2.

La DC6024/3 usa una memoria de núcleos magnéticos, una estructura "bus" de acceso múltiple. Las operaciones aritméticas son sobre la base de complemento dos y se dispone además de multiplicación/división/raíz cuadrada en Hardware. Se incluye también 5 registros de 24 bits de propósitos generales, tres de los cuales pueden ser usados para indexado.

El acceso a memoria es a nivel de palabra (word), doble palabra (double-word) y byte (8 bits), de modo directo, indirecto o indexado.

1-2 Software. — Se dispone de un Sistema Operativo de cinta magnética (TOS), compilador FORTRAN IV, librería FORTRAN; MACRO ASSEMBLER; ASSEMBLER; Diagnóstico de Hardware, Paquete de Utilidad, DEBUG, etc.

Las instrucciones de ASSEMBLER son poderosas y versátiles, y permiten manipulaciones de registro-registro, registro-memoria y viceversa; además de operaciones lógicas, aritméticas, control de interrupciones y funciones de entrada/salida en base al reconocimiento de casi 600 instrucciones mnemónicas.

#### 2 SISTEMA DE ENTRADA Y SALIDA

#### 2-1 Introducción

Se enlazan los sistemas I/O (entrada/salida) de la unidad periférica con los del CPU por medio de un canal que ofrece máxima flexibilidad y rapidez.

La transferencia de datos puede ser de palabra de 24 bits en palabra a través de la estructura básica de I/O. En este caso la transferencia puede ser controlada con un "software" apropiado (control programado).

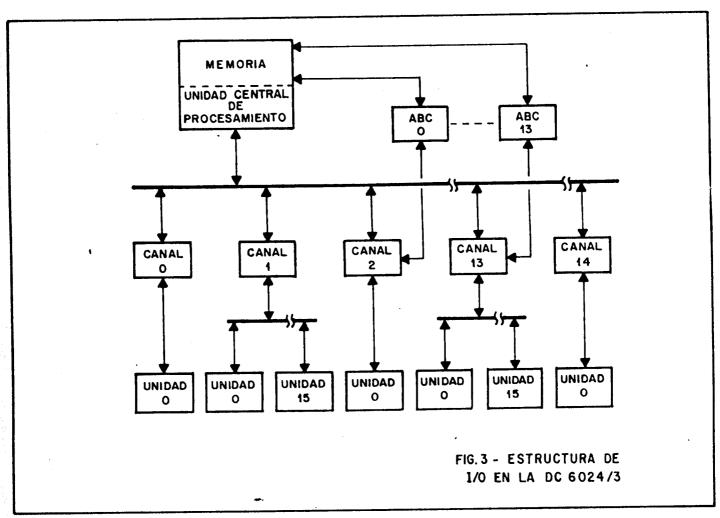

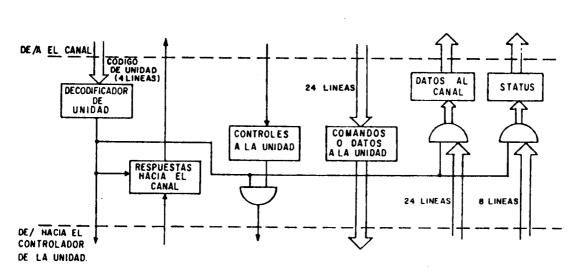

También es posible transferir datos por bloques, esta vez sin control por programación salvo para la inicilización usando un ABC. El esquema representativo de la estructura I/O se muestra en la Fig. 3.

En la estructura básica I/O el CPU se comunica con un canal y éste a su vez lo hace con una unidad periférica. Pueden haber un máximo de 14 canales todos activos a la vez y un máximo de 16 unidades periféricas por canal. Al decir activos se entiende que pueden estar operando simultáneamente; sin embargo, se aclara que el CPU puede atender unicamente un canal a la vez y cada canal una unidad, pese a que el resto esté operando de algún modo por su cuenta.

Usando el control automático de bloques se podrían transferir bloques de palabras de 1 a 65,536 en forma automática, a una velocidad máxima de 500,000 palabras/seg. (1.5 millones de bytes). Pueden existir hasta 14 ABCs operando simultáneamente, pero en conexión con el CPU y memoria solo uno a la vez.

COMPUTADORA DC 6024/3

#### 2-2 Clasificación de las Comunicaciones

Las comunicaciones entre el CPU y la combinación canal/unidad seleccionada se hacen a través de un registro llamado "A" en el CPU y los correspondientes receptores en el canal o/y unidad llamados "Buffers".

Estas comunicaciones pueden consistir en la transferencia de comandos, datos y estados (status).

Los comandos indican a la unidad periférica acciones a tomar sean estas mecanicas o electrónicas. Los datos son simplemente información numérica binaria que se envía al periférico o se recibe de él (casos del DAC y ADC). Los status son información recibida del periférico respecto de su situación y condiciones de operación. Finalmente se requiere información de dirección de palabras cuando se usa un ABC, pues es necesario saber, dónde está ubicada la primera palabra del bloque en memoria y la cantidad de palabras —sea en entrada o salida de datos— a transferirse usando este dispositivo; esta información sin embargo, no llega al periférico sino que se mantiene en dos registros del CPU.

El establecimiento de estas comunicaciones se hace a través de instrucciones apropiadas en lenguaje Assembler básico como son "OCW" (comandos); "IDW" o "ODW" (datos), etc.

Intermedio entre las instrucciones y la respuesta del periférico avisando del establecimiento de la comunicación existen una serie de señales que precisamente serán tema de estudio en este trabajo en acápites posteriores. Esto último está relacionado directamente con la interfase y el controlador tema central de este trabajo.

#### 2-2.1 Transferencia de Comandos

Se realizan a través de la instrucción OCW (Output Command Word) especificando el canal y unidad afectados.

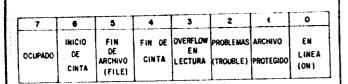

Los comandos u órdenes mismas van en la llamada palabra de comando proveniente del registro A (24 bits). Los bits 0-2 se utilizan para el control del sistema de interrupción de la unidad. En el resto de bits van los comandos propiamente dichos que varían de una unidad a

Un sistema de interrupción permite "interrumpir" las labores del CPU (normalmente procesando, etc.) para que atienda un llamado de la unidad que pide entregar u obtener un dato a/o de memoria.

Como ejemplo típico de una palabra de comandos tomamos el cinta magnética en la Fig. 4 donde se explica brevemente el su,....cado de cada bit.

#### 2-2.2 Transferencia de datos

- Entrada: Con la instrucción IDW (Input Data Word), la cual es un pedido del CPU a un canal/unidad específicos de un dato; que en caso de estar disponible se transfiere al registro A en el CPU.

- Salide: Se usa la instrucción ODW (Output Data Word) y su ejécución implica la transferencia de un dato del registro A al correspon-

diente buffer de un canal (este a su vez transfiere posteriormente este dato a la unidad periférica).

Los datos pueden ser números binarios o símbolos con un cierto código en binario, códigos que pueden emplear un número variable de bits por símbolo o caracter (letras, números, etc.), según sea el tipo de unidad (lectora de tarjeta, teletipo, etc.). La transferencia sea de entrada o salida es hasta un máximo de 24 bits a la vez (una palabra).

#### 2-2.3 Transferencia de Status

Con la instrucción ISW (Input Status Word) que permite el acceso al registro A del CPU del status de la unidad periférica.

Casos típicos de palabras de datos y status son los de la Fig. 5.

#### 2-3 Funcionamiento de un canal de I/O

El canal representa una parte fundamental en las comunicaciones de I/O y por ello es conveniente tener un concepto simple pero claro acerca de su funcionamiento.

Como ya se mencionó, éste sirve de enlace entre la computadora misma (CPU) y la unidad periférica; pero, el principal objetivo que persigue es el de "independizar" precisamente a estos dos. Existen periféricos "lentos" como por ejemplo la lectora de tarjetas, teletipo, etc., y a su vez "rápidos" como la cinta magnética, disco, etc.; el CPU debe entenderse con todos en lo que respecta a entrada/salida de datos y comandos. Es decir, unos tomarían más tiempo de computadora que los otros, si es que ésta se dedicara a atender exclusivamente a cada uno hasta su terminación; además del problema de sincronismo.

Por este motivo es que el CPU atiende a cada uno de ellos, sólo cuando éstos estan preparados para recibir o entregar los datos, comandos, etc.; y mientras tanto es el canal el que se preocupa del resto permitiendo que se aproveche con máxima eficiencia el tiempo de computadora. Es decir mientras el CPU está realizando otras tareas (cómputos en general), el canal prepara las condiciones para la transferencia de un dato o bloque de datos (ABC) u comandos etc. sin interferir con el CPU.

Esto lo realiza mediante funciones independientes del CPU y con el auxilio (aunque no necesario) del sistema de Prioridades e Interrupciones.

El Sistema de Prioridad, como su nombre lo dice, jerarquiza las preferencias en cuanto I/O de los periféricos. Esto es, decide quién tiene preferencia a ser atendido por el CPU.

El Sistema de Interrupciones consiste de señales llamadas "interrupts" intercambiadas entre canal/unidad y canal/CPU que comunican a el CPU que un determinado canal/unidad está listo para recibir o entregar un dato (o bloque de datos con el ABC). Estas señales paralizan momentaneamente al CPU en sus funciones y transfieren el control de este último a un "Procesador de Interrupciones" (en software) el cual decide la acción a tomar. (véase 2-6.2 y 2-6.3).

FIG. 5. (a) PALABRA DE STATUS

UNIDAD DE CINTA MAGNETICA

NUMERO BINARIO 2'

FIG. 5. (b) PALABRA TIPICA DE DATOS

La rutina de procesamiento de interrupción normalmente, salva el contenido de los registros y la dirección en que fue interrumpido el programa anterior que el CPU estuvo procesando; identifica la causa de la interrupción y decide sobre salida o entrada, u otra acción diferente, como es el caso cuando la interrupción es generada para indicar fallas u otros en la unidad periférica.

El "Procesador de Interrupciones" incluye instrucciones de ODW y/o IDW para la entrada y/o salida de los datos.

En el trabajo, tema de esta tesis no se ha hecho uso del sistema de interrupción puesto que las instrucciones de I/O se ejecutan dentro de un Programa controlador (en software) que espera a que la unidad periférica (Display XY) reciba los datos que necesita, requiriendo atención exclusiva del CPU durante este tiempo. Aunque esto no resulta muy eficiente, basta para nuestros propósitos ya que este periférico es bastante rápido.

Es conveniente resaltar que el CPU entrega o recibe el dato del canal y luego se desentiende y regresa el control al programa en proceso. Es el canal el que finalmente realiza la transferencia con la unidad periférica.

El programa en proceso sin embargo, puede ser uno que monitorea constantemente el status del canal/unidad como es el caso de la transferencia programada (2-6.1), u otro que espera recibir una señal de interrupción para realizar una transferencia (2-6.2).

#### 2-4 Operación de la Interfase de Entrada/Salida

En esta sección se tratará el funcionamiento u operación de entrada y salida de la computadora DC6024/3. Dicha operación se refiere a la transferencia de datos, direcciones, comandos e información de status entre el CPU y las distintas unidades periféricas. Ahora bien las transferencias se consiguen a través de los canales y la interfase de I/O. El canal controla el flujo de la información y la interfase sirve de eslabón entre este último y la unidad periférica misma.

Las señales de información intercambiadas entre el canal y la unidad periférica a través de dicha interfase son estandard. En el caso del presente trabajo sólo se ha hecho uso de ellas, sin intentar modificar ni agregar nada.

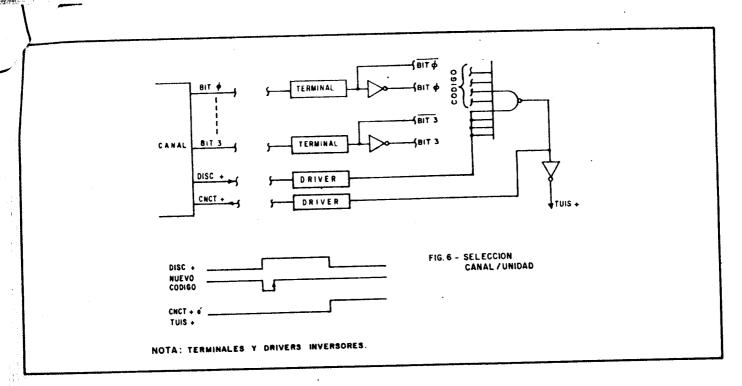

#### 2-4.1 Selección de canal y unidad

Las instrucciones de I/O en Assembler continene una especifi-

cación del canal y unidad a usarse, 5 bits para el canal y 4 para la unidad. Cada vez que se ejecuta una de estas instrucciones (IDW, OCW, etc.), el CPU presenta el código de canal/unidad a el canal, el cual reconoce el llamado y responde con una señal (THIS CHANNEL IS SELECTED). Esta señal permite al canal résponder e identificar los controles del CPU.

A continuación el código de la unidad es depositado en sendas líneas de interfase (4 bits) a través de Drivers, y recibido al otro extremo en la tarjeta de Interfase de la unidad por circuitos terminales inversores, pasado a una red decodificadora (NAND), que en caso de reconocerlo envía una señal al canal (CONNECTED) indicando su conexión.

Mientras una unidad esté operando con el canal correspondiente, éste, la mantendrá en la condición de "conectada". Cuando el canal requiere de una unidad diferente, éste envía el pulso de "DISCONNECT" a la unidad en ese momento conectada y simultáneamente el nuevo código de unidad: Al ser reconocido por la correspondiente unidad responde nuevamente esta última con un pulso de CONNECTED y genera otro pulso para uso interno (THIS UNIT IS SELECTED) que le permite aceptar posteriores comandos o datos y responderlos si así es necesario.

Un diagrama sintético incluyendo lógica y secuencia de tiempo de estas señales es el de la Fig. 6.

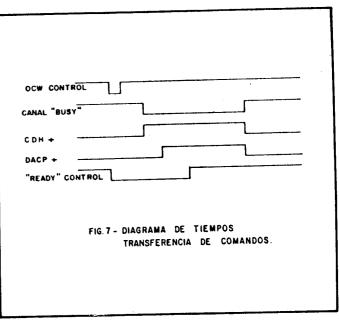

#### 2.4.2 Transferencia de Comandos

La instrucción OCW cuando es ejecutada, produce la transferencia de una palabra de comando (24 bits) del registro A en el CPU a través del canal e interfase (24 líneas) a la unidad correspondiente (seleccionada). Estas señales aparecen simultáneamente con una de COMMAND DATA HERE (CDH) en la unidad periférica, la cual luego de recibirlas produce una señal de OUTPUT DATA ACCEPTED (ODACP) hacia el canal que da por terminada la transferencia. El canal mientras dura la transferencia señala ocupado (BUSY) al CPU hasta que la unidad le responda.

Los bits de comando proporcionan la información necesaria al periférico, acerca de una acción mecánica, electrónica, etc. requerida. Por ejemplo la selección de entrada o salida en el sistema de interrupciones en unidades capaces de ejecutar ambos.

El diagrama de tiempo simplificado de la secuencia se muestra en la Fig. 7.

## 2-4.3 Transferencia de datos (Una palabra de dato a la vez) Modo I/O básico:

- Selida: Después de ejecutada la instrucción ODW (Output Data Word) se transfiere una palabra datos (24 bits) del registro A en el CPU hacia la unidad periférica a través del canal e interfase. Estos datos van acompañados de la señal OUTPUT DATA HERE (ODH) y una vez aceptados por la unidad, esta última responde con un OUT-PUT DATA ACCEPTED (ODACP).

- Entrada: Cuando se requiera ingresar datos del periférico hacia la computadora (registro A del CPU), la unidad periférica deberá generar la señal DATA AVAILABLE FROM UNIT (DAVFU) y entregarla al canal junto con los datos en las líneas de Interfase correspondiente. A continuación queda a la espera de la ejecución de la instrucción IDW (Input Data Word) por parte del CPU; una vez ejecutado el IDW y estando presente el DAVFU recién se procede a la transferencia, que una vez terminada es respondida con una señal de DATA ACCEPTED hacia la unidad.

#### NOTA:

En cualquiera de los casos anteriores podría ocurrir que cuando se ejecuta la instrucción de I/O, el canal aludido estuviera ocupado en una transferencia anterior aún no concluída. En estas circunstancias no da a lugar la nueva instrucción de I/O y el canal responde con una señal de BUSY al CPU, colocando al llamado "registro de condición" en la posición de "negativo".

El "registro de condición" tiene 4 bits (overflow, positivo, negativo y cero); está ubicado en el CPU y sirve para monitorear las diferentes etapas en el proceso interno de cálculo de la computadora. En este caso sirve para saber si el canal está ocupado o no.

#### 2.4.4 Transferencia en Bloques

Realizada mediante un ABC. Aunque es un tema muy interesante no entra dentro de los alcances de este trabajo pues no se usa. Básicamente consiste en la transferencia de palabras "robando" un ciclo de CPU por cada una.

#### 2-5 Control de Interrupciones

Son básicamente de dos tipos:

a. — Interrupción de entrada — Cuando está activada, es la señal DAVFU la que da la orden de interrupción (véase "Funcionamiento de un canal en I/O").

b.— Interrupción de salida — Cuando está activada, el canal da la orden de interrupción apenas termina de entregar un dato a la unidad, o bien la unidad puede dar la orden a través del bit 2 de la palabra de status; esto según el pulso ECBI (Enable Channel Buffer Empty) esté en 1 6 0.

Todas estas posibilidades de interrupción están en los tres primeros bits de cualquier palabra de comando de acuerdo a:

bit  $\phi$ : activar/desactivar la interrupción de entrada

bit 1 : activar/desactivar la interrupción de salida

bit 2 : ECBI (explicada arriba)

Esto es un resumen muy corto, pero no es necesario tenerlo muy en cuenta puesto que en este trabajo no usamos el sistema de interrupciones (véase "Funcionamiento de un Canal en I/O").

#### 2-6 Resumen

Las ideas acerca del sistema de entrada y salida están un tanto dispersas hasta el momento; ahora se tratará de clarificarlas y ordenarlas en forma abreviada.

No se entrará en detalles y más bien el lector deberá referirse a acápites anteriores para ello, o en todo caso consultar el lúcido reporte de la referencia bibliográfica 4.

#### 2-6.1 Transferencia con Control Programado

Este modo requiere el mínimo de Hardware pero en cambio necesita de un monitoreo constante por parte del CPU. Cuando se inicia la transferencia, el CPU chequea en todo momento, cuando el canal ha recibido el dato u comando y cuando está listo para aceptar una nueva transferencia (esto ha sido llamado I/O básico). Con este fín, intercambian una serie de señales el canal y CPU.

En general la transferencia consistirá de comandos, sensados (status) y datos (en entrada o salida) del modo ya explicado en los acápites 2-2 y 2-4.

El monitoreo del CPU y transferencias mismas, estarán regidos por un programa de control (Software) que es una parte important (sima del sistema.

Nótese que éste es el modo escogido para el presente Proyecto.

#### 2-6.2 Transferencia Controlada por Interrupciones

Este modo implica una lógica (Hardware) más compleja que la anterior. En este caso, el CPU es responsable de iniciar el "proceso" y, luego, son el canal e interfase los responsables de avisar al CPU cuándo ejecutar la transferencia.

El caso típico consistiría en que el CPU a través de un progra-'principal" determinaría cuándo es el momento de transferir un ato o bloque de datos a algún periférico. El mismo CPU inicia el proceso" enviando comandos adecuados que activan señales de "inrrupción" del periférico, contadores, etc.; a continuación el CPU ontinúa en otras labores (cómputos en el programa principal por emplo), y deja al canal correspondiente monitoreando al periférico sando la interfase como medio. Cuando el controlador del periférico etermina que éste, está listo para realizar la transferencia, la interfase enera un "pedido de interrupción" que cruzando el canal llega al PU.

El CPU al recibir este pedido, paraliza la tarea que realiza, y ilta a la rutina llamada "Procesador de Interrupciones" (véase 2-3 y 5) aue efectúa la transferencia, se pone al día (en cuanto a número ferencias efectuadas por ejemplo), y finalmente regresa a la rea que se estuvo efectuando al momento de la interrupción hasta 1 nuevo pedido, donde se repite la secuencia.

Las ventajas de este modo son evidentes. (véase 2-3 y 2-5).

#### 6.3 Transferencia con Control de Acceso Directo a Memoria

Como el nombre lo dice, la interfase por medio de un canal BC transfiere el dato directamente a la memoria del CPU (en los isos anteriores fue al registro A).

El CPU inicia el "proceso", suministrando los datos de direcón de memoria, y número de palabras a transferirse, a dos registros oveidos con este fin por la DC6024/3, y CPU continúa en otras reas. Cuando el periférico está listo para la transferencia, el CPU nplemente se detiene por un ciclo de máquina (1 µ seg) - "roba" 1 clo - y ésta (la transferencia) se realiza en forma tal que no afecta en ida las tareas del CPU (salvo el µseg de para); poniendo simulneamente al día a los registros de dirección y número ya mencionais arriba en una suerte de compartición de tiempo (time sharing). De te modo se consiguen altas velocidades de transferencia en paralelo n el procesamiento.

Desde el punto de vista de eficiencia, esto es lo ôptimo pero quiere de un Hardware mas complicado que el de los dos casos teriores.

Aquí también se usan las señales de interrupción del caso anteir, pero a diferencia de este último, solo para indicar, que la transfencia del bloque en conjunto ha sido concluída, y no por cada dato.

La Fig. 8 muestra un diagrama de bloques de una interfase

#### DISEÑO E IMPLEMENTACION DEL SISTEMA DE DESPLIEGUE VISUAL X-Y (DISPLAY X-Y)

El objetivo principal de este trabajo es el diseño de un controlor para el barrido de una pantalla de rayos catódicos (display), que dría ser un osciloscopio en principio, de modo de obtener una ágen gráfica y casi instantánea de algún proceso efectuado en la mputadora el cual se requiere monitorear.

- Los criterios usados en este diseño son:

- Máximo aprovechamiento de las facilidades de interfase que brinda la DC6024/3.

- El tiempo de computadora utilizado en controlar esta nueva unidad periférica debe ser mínimo (máxima eficiencia).

- Flexibilidad de diseño, esto es, debe permitir varias alternativas de uso y modificaciones de acuerdo a nuevas necesidades futuras.

- Modularidad y presentación en su construcción.

De acuerdo al primer criterio, se ha utilizado la tarjeta convencional de interfase diseñada por la Datacraft para este fín, y las especificaciones recomendadas para la interconección canal-unidad periférica.

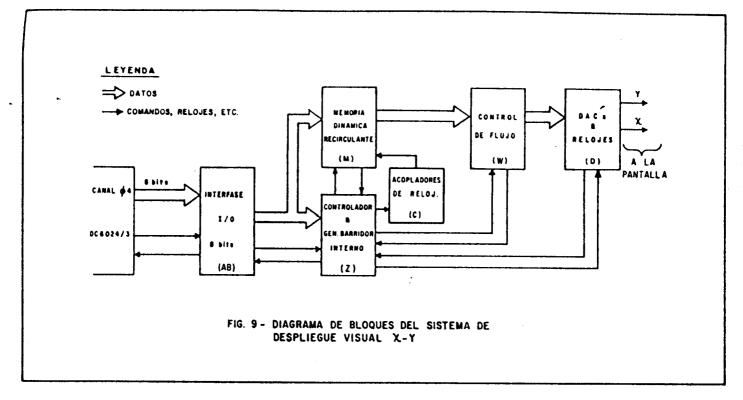

Según el segundo criterio, dado que para visualizar un gráfico en una pantalla y mantenerlo, es necesario repetir las señales que lo originan (barrido continuo), se utiliza, una memoria auxiliar que almacene los datos a graficarse y los reponga continuamente sin necesidad de la computadora, salvo para adquirir nuevos datos. A su vez la carga de nuevos datos se hará a máxima velocidad.

El punto tercero, produce como consecuencia nuevas alternativas de uso. Además de un display para graficar Y vs X, debe servirnos también para graficar Y vs tiempo generando internamente el barrido horizontal (diente de sierra) o simplemente como un conversor digital -análogo. (Un experimento útil sería por ejemplo digitalizar voz con un conversor análogo-digital, luego simular un proceso sobre esta voz con la computadora, para posteriormente pasarla por un DAC (nuestro tema) observando los resultados o consecuencias en la voz de salida final). En realidad el corazón del sistema lo constituye precisamente el conversor digital-análogo.

En cuanto al cuarto criterio, solo mencionaremos ahora el hecho de haberse utilizado técnicas modernas de construcción; más adelante se ampliarán detalles.

#### Diagrama y Funcionamiento en Bloques del Sistema

Recopilando algunos puntos ya mencionados en el acápite anterior. Tenemos que se usa una memoria auxiliar que de ahora en adelante se llamarà memoria dinámica recirculante (MDR) por razones que serán claras posteriormente; tarjetas estandard de interfase canalunidad; además del controlador propiamente dicho, generador de barrido (diente de sierra) y relojes.

Un diagrama de bloques del sistema sería el de la Fig. 9.

Operación

Procedentes y hacia la computadora se tienen líneas de datos y de comando, órdenes de interrupción, respuestas de la unidad y otros.

#### 3-2.1 Interfase

Que no es más que una serie de terminales que acoplan la impedancia de las líneas que vienen del canal hacia la unidad periférica; las señales pasan hacia el controlador propiamente dicho y a la MDR. Además las señales que regresan a el canal lo hacen por medio de ',drivers' que proporcionan un nivel adecuado de intensidad y acoplamiento a las líneas. Estos últimos también se encuentran en la etapa de interfase.

FIG. 8 - DIAGRAMA DE BLOQUES DE LA INTERFASE.

#### 3-2.2 Controlador

Es el que traduce los comandos y proporciona las respuestas requeridas por la computadora, además decide sóbre las órdenes a efectuar como por ejemplo cargar nuevos datos en la memoria auxiliar, o MDR, o hacer las recírculación.

#### 3.2.3 Memoria Dinâmica Recircularite

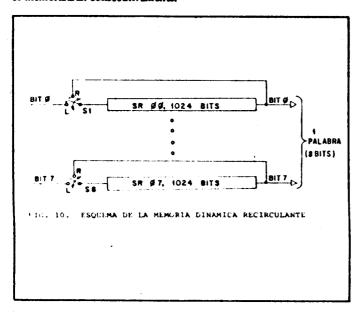

Consiste de 8 shift registers (registros de corrimiento) de 1024 bits cada uno trabajando en forma paralela, de modo que en un tiempo determinado y fijo se tienen 8 bits de datos a la vez. Esta situación se ilustra en la Fig. 10. Observamos a su vez que según el estado de los interruptores S1 a S8 estos datos pueden hacerse recircular (posición R) o en todo caso renovar (posición L). De este modo, pués podemos mantener una imagen fija en el display (recirculación) o cambiarla (renovación o carga). La capacidad de almacenamiento de la MDR es pues de 1024 palabras de 8 bits cada una.

Se utilizarán pues en el presente diseño, datos de 8 bits (la tercera parte de la capacidad de una palabra de computadora). En el caso de usarse la alternativa de un display X-Y los datos de X y de Y se memorizarán consecutivamente.

#### 3-2.4 Control de Flujo de Datos

Tiene la misión específica de transferir los datos de la MDR hacia los convertidores digital-analógico. Una de sus funciones es por ejemplo entregar los datos de X y de Y que vienen secuencialmente en el tiempo desde la MDR, en forma simultánea a los DACs; así se consigue una reproducción fiel de los datos en el display.

#### 3-2.5 Convertidores Digital-Análogo

Circuitos híbridos (semi integrados) cuya salida es la representación análoga del número binario (10 bits) en sus entradas. Se utilizan en número de dos, uno para X o barrido interno y otro para Y.

#### 3-2.6 Generador de Barrido Interno

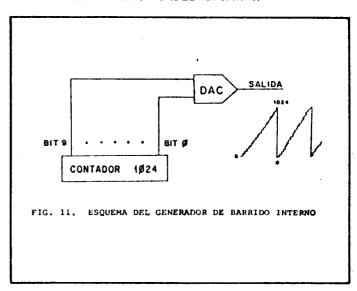

Se obtiene un diente de sierra de periodo igual al de recirculación de la MDR mediante un contador de módulo 1024 cuyas salidas entran a un DAC (véase Fig. 11).

En todo caso el DAC usado es el mismo del X anterior, o sea se usa o bien la alternativa X-Y o Y vs Barrido Interno.

#### 3-2.7 Relojes

Se utilizan dos relojes cada uno de dos fases. Un reloj de frecuencia alta (casi 2 MHz) para una rápida carga de datos de la computadora a la MDR (mínimo tiempo de computadora). Otro reloj de baja frecuencia adecuada para la visualización sin molestias del display (sin parpadeos).

#### 3-2.8 Pantalla

Originalmente un osciloscopio, aunque se piensa disponer de uno más estandard.

#### 3-3 Descripción Detallada de los Circuitos

Las diferentes partes presentadas en el diagrama de bloques de la Fig. 2 se distribuyen en 6 tarjetas construídas para tal efecto. Un resumen de dichas tarjetas en cuanto a su contenido y características se presenta en la Tabla I a continuación:

| Permit e                                    | Contenido                         | Identificació: |

|---------------------------------------------|-----------------------------------|----------------|

| interface 1/0<br>canal-unided               | Circuitos termineles<br>y drivere | AB             |

| Remotta dinămi-<br>că ivcirculante          | Requetros de Corri -<br>Biente    | No.            |

| Acopladores de<br>pulsos de reloj           | Amp, Transistorisado<br>de pulsos | •              |

| Control de flu-<br>jo de datos de<br>salide | FFs, gates, stc.                  |                |

| Controledor                                 | Controlador, genera-              |                |

| Convertidores<br>digital-análogo            | 3 DACe à tejoise                  | Þ              |

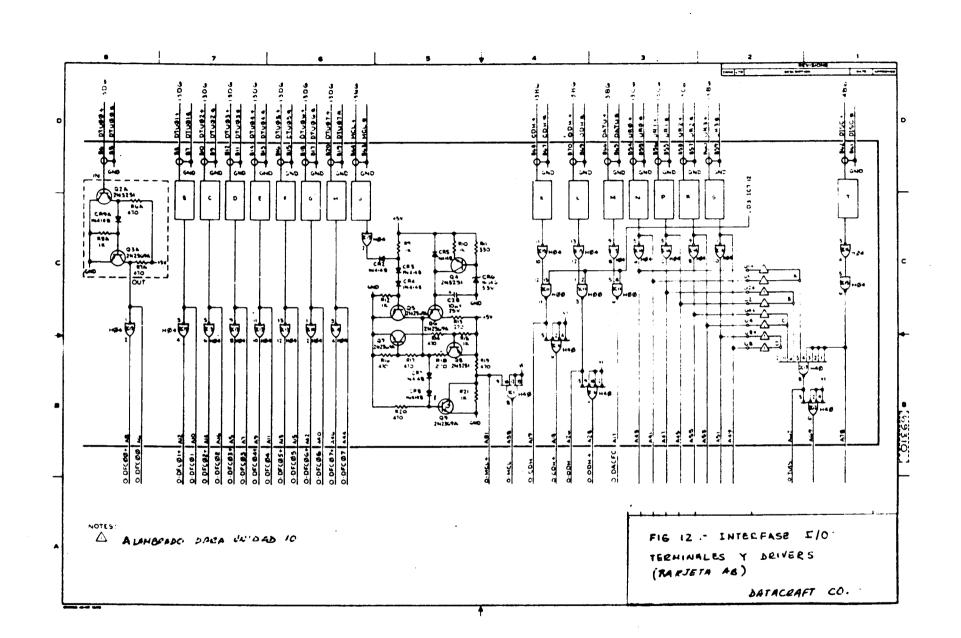

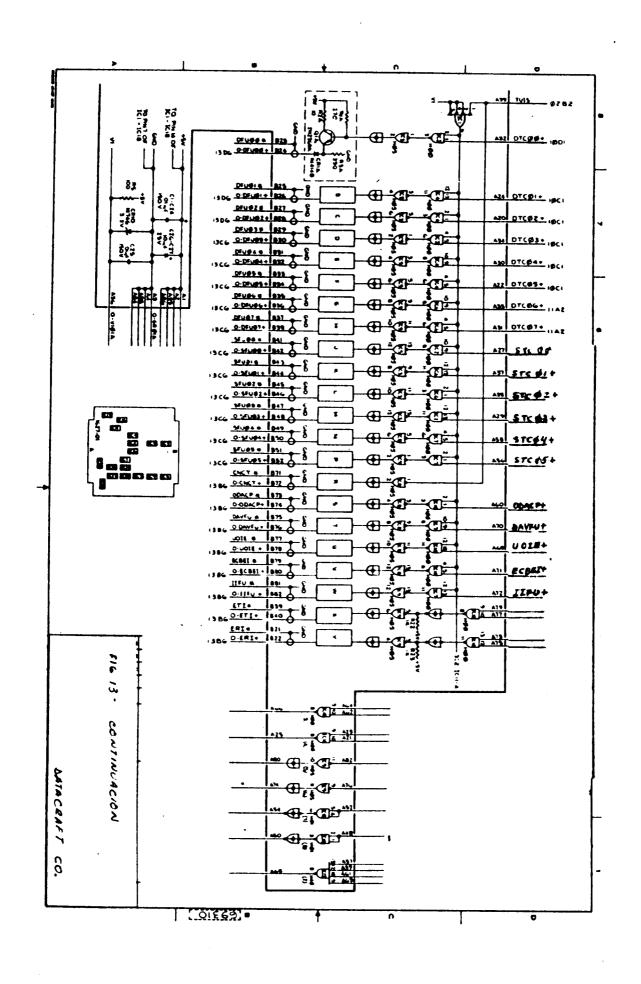

#### 3.3.1 Interfase

Esta tarjeta confeccionada bajo las técnicas de circuito impreso, y cuyo esquema eléctrico ha sido realizado por la Datacraft Corporation, se muestra en las Figs. 12 y 13.

La manera de entender las principales convenciones adoptadas en estos planos es como sigue: Los gates en una misma designación (IC1, IC2, etc) son de un mismo Circuito Integrado, (mismo "chip"). Los pequeños números en las entradas y salidas de los gates corresponden físicamente a la "patita" del "chip" (Circuito Integrado).

Esta tarjeta tiene dos extremos cada uno de ellos con 86 contactos. A uno de estos juegos de contactos se le designa A y a el otro B. Así donde aparece, por ejemplo A40, esto quiere decir contacto 40 extremo A.

Se utilizan además abreviaciones mnemónicas de las señales, por ejemplo ODACP+ indica "Output Data Accepted" y el signo +, que el nivel normal es "O" apareciendo un "1" en la condición "ON". de dicha señal. Una explicación más detallada de estas señales, su abreviación y su uso se describe más adelante (Ver Apéndices).

Importante es distinguir y resaltar que la lógica usada en ésta y demás tarjetas es TTL (Transistor Transistor Logic) salvo pocos casos, que se mencionarán a su tiempo.

Otras convenciones en el gráfico son fáciles de comprender o no interesan para nuestros propósitos.

En la Fig. 12 los bloques B, C..., T son similares al circuito A, terminal que acopla la impedancia de la línéa proveniente del canal de la computadora (100 ohm) y repone los voltajes normales correspondientes a los niveles 0 y 1 (0 y. 5 volt) que llegan atenuados por la longitud del cable.

Existe un circuito especial para la señal MCL (master Clear) que maneja gran cantidad de gates y por lo tanto requiere suministrar apreciable corriente.

En la Fig. 13 de igual modo los bloques B.,.., Y similares al A, sirven de "drivags", siendo acopladores de impedancia y proporcionando una corriente adecuada. Los integrados IC3, IC5, IC8 e IC9 son del tipo colector abierto (open colector) que son usuales en esta aplicación de interfase; pues permiten, colgar varios periféricos a las mismas lineas de interfase, mediante un encadenamiento (daisy chain) y a través de alambrados o empalmes "or" (en Inglés "tied or") de las salidas de este tipo de elementos.

Una lista de los elementos utilizados en el ensamble de esta tarjeta y las próximas, aparece en la sección acerca del montaje y el diagrama de bloques en la Fig. 8.

Tablas de la ubicación de las señales en las Tarjetas se encuentran en la sección 3-5.

Los siguientes parrafos definen las señales estandard presentes en la interfase canal/unidad (Ref. 2).

#### - Señales de salida

A. Master Clear (MCL+)

Esta señal sirve para establecer condiciones iniciales de operación en la estructura I/O; y se aplica, cuando la potencia es conectada o desconectada, o cuando se presiona el interruptor correspondiente sobre la consola de la Computadora.

- B. Código de Unidad (UR+ hasta UR3+) Conformado por 4 líneas que llevan el código de 4 bits y son usadas para seleccionar la unidad apropiada en la operación de U/O.

- C. Bits de Datos o Comandos de Salida (DTUOO+hasta DTU23+) Estas 24 líneas proporcionan sendos bits de una palabra de datos o comandos.

- D. Output Data Here (ODH+)

- Esta señal generada a la vez que las anteriores (C) indica que la información en C forma una palabra de datos y no de comandos.

- Comand Data Here (CDH+)

- Significa que la información en C forma una palabra de comando y no de datos.

- F. Disconnect Unit (DISC+)

Para su uso véase (2-4.1).

G. Input Data Accepted (DATU+) Indica que el canal ha recibido y aceptado una palabra de datoa proveniente de la unidad (ver párrafo D de "Señales de Entrada").

#### - Sañales de Entrada

A. Unit Connected (CNCT+)

Por medio de esta señal la unidad avisa que ha recibido y reconocido el código de unidad.

B. Data Accepted (DACP+)

Avisa la unidad que ha recibido y aceptado una palabra de datos o comandos de el canal.

C. Input Data Available (DAVFU+)

Indica que el periférico tiene una palabra de dato lista para la transferencia.

D. Input Data Bits (DFUOO+-DFU23+)

24 líneas de Datos hacia el canal.

E. Status Bits (SFUOO+-SFU07+)

8 líneas de status según lo explicado anteriormente.

#### - Señales de Control de Interrupciones

A. Output Interrupt Enabled (UOIE+)

Indica que la interrupción de salida de la unidad se selecciona. Esto no significa un pedido de interrupción.

B. Input Interrupt Request (IIFU+)

Pedido de interrupción de entrada a la computadora avisando de un dato en la unidad, listo para la transferencia.

C. Enable Buffer Empty (ECBI)

Indica que la interrupción de salida se generará según lo explicado en la pag. 11.

Estas señales se reparten en 2 tarjetas propuestas por la Datacraft Corporation, siendo la principal la primera que contiene los primeros 8 bits de datos de entrada y salida, 5 bits de status, interrupciones y el resto de señales.

La segunda tarjeta contiene el resto de bits de datos y de status.

¡En este proyecto solo se usa la primera!

#### 3-3.2 Memoria Dinámica Recirculante

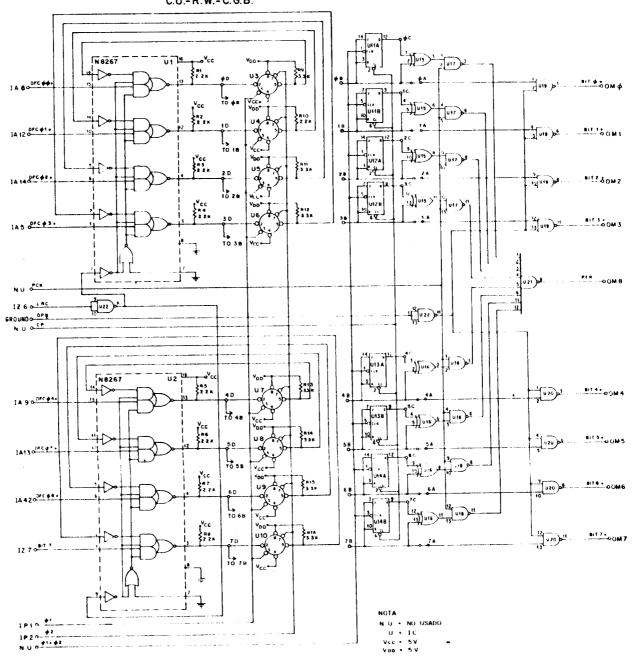

En esta tarjeta hecha bajo técnicas de circuito impreso, montada con Circuitos Integrados MSI (Signetics 8267), LSI (Intel 1402) TTL y MOS respectivamente, se pueden almacenar una matriz de 1024 x 8 datos de 1 bit.

En la Fig. 14 se muestra el esquema de la MDR. Se muestran claramente las entradas de los 8 bits de datos que realmente han viajado ya del registro A del CPU al canal apropiado y de este último a la tarjeta de Interfase. Es decir, los datos (8 bits) que en número máximo de 1024 podrán ser almacenados en la memoria.

Los multiplexers (IC1 y IC2) cada uno de 4 bits permiten seleccionar entre datos provenientes de la computadora (nuevos) o hacer recircular los ya almacenados, conservándolos y reponiéndolos constantemente en la salida. Esta selección se hace controlando la señal LRC (Load-Recirculate); el nivel "O" significa carga y el "1" recirculación. IC1 e IC2 son del tipo "colector abierto" de allí las resistencias R1-R8 [6].

Los registros de corrimiento (IC3 a IC10) constituyen a fin de cuentas la memoria. Estos son fabricados por Intel con la denominación 1404 MOS Dynamic Memory (5) tienen una capacidad de 1024 bits y trabajan con un Reloj de 2 fases (entradas IP1 - IP2  $\phi$ 01,  $\phi$ 2). Las resistencias R9-R16 son requerimientos de fabricación.

Estas memorias son dinámicas, es decir necesitan constantemente de un "refresco" de modo que no se extingan los bits almacenados. Esto impone restricciones en la frecuencia mínima del Reloj en 400 Hz a condiciones ambientales de temperatura (25°C); a mayor temperatura mayor frecuencia mínima [5].

Igualmente se tiene un límite en la frecuencia máxima (4 MHz) según indicaciones de los fabricantes.

La transición negativa de Reloj determina el corrimiento o avance de 1 bit a la derecha en la memoria, mientras que la positiva la carga o aceptación de un dato en la entrada, sea este de recirculación o uno nuevo, nótese la Fig. 15. Es necesario que los pulsos de las dos fases de Reloj sean alternativos, caso contrario pueden suceder errores de grabación o reproducción.

IC10 e IC20 sirven para inhibir las salidas (OM $\phi$ -OM7) cuando así se desse con el control DPY. El resto de gates se usan en otro proyecto, y sirven para un control de paridad de los bits grabados, indicándose el error en la salida PER.

Resumiendo: Se disponen de 8 entradas que dan acceso a sendos bits de datos del CPU, se pueden grabar o memorizar 1024 de estos, y finalmente se tienen 8 salidas. Se pueden cargar nuevos datos o recircular los ya grabados con un comando apropiado.

ď

Aalo<sup>s</sup>

#### RECIRCULATING DYNAMIC MEMORY 1024 WORDS x 8 BITS C.U.-R.W.-C.G.B.

FIG 14 .- MEMORIA DINAMICA RECIRCULANTE (TARJETA M)

Nº2.525 JK AM 25/eget /74 CU-RW-C G B /MINM

# CARGA CARGA AVANCE AVANCE BIT N BIT N+1 BIT N+2 BIT N+3 BIT N+4 FIG. 15. FASES DE RELOJ EN LA MDR

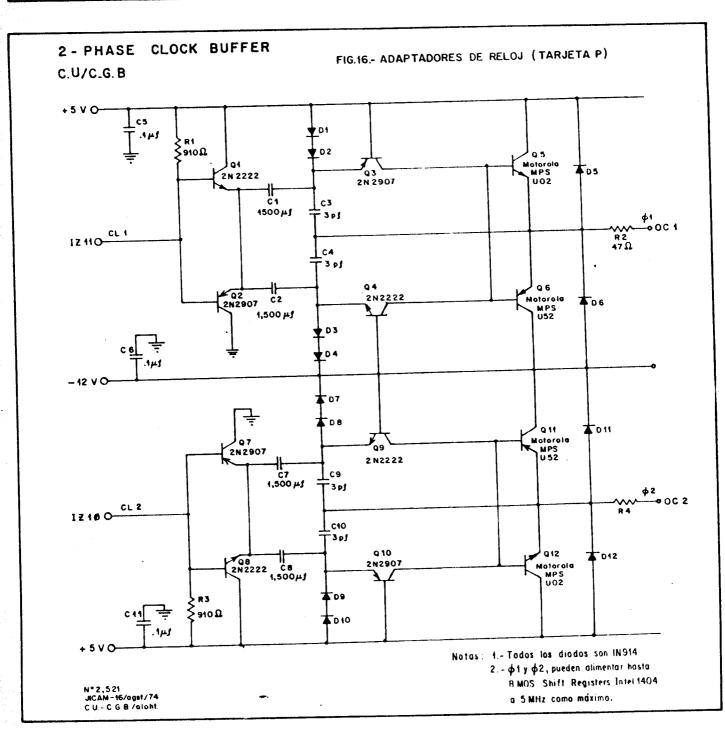

#### 3-3.3 Adaptadores de pulsos de Reloj

El uso de los Circuitos Integrados Intel 1404 en la Tarjet. MDR impone por razones de fabricación el uso de relojes cuyo estac. "1" (alto) sea de 5 volt. y de "0" (bajo) de -12 volt. El tiempo de subida y bajada en estos pulsos así mismo ha de ser mínimo, si no se quiere limitar la frecuencia.

Por estas razones se hace imperativo el uso de un adaptador de pulso de la lógica 74/TTL usada en el resto del circuito (0v,-5v) con los relojes para el MDR (-12v,-5v). Las características de este adaptador (Clock Buffer) han de ser su rapidez, fan out o capacidad de manejar hasta 8 integrados 1404 (número usado en la MDR) y lógicamente la salida con los voltajes apropiados.

Según recomendaciones de Intel Co. el circuito usado corresponde al de la Fig. 16.

En dicha figura se muestran dos de estos adaptadores, armados en una misma tarjeta en circuito impreso, usándose uno por cada fase de Reloj según lo expuesto en 3-3.2

Los transistores Q1 y Q2 trabajan de modo que mientras uno se corta el otro se satura en armonía con la entrada, teniendose en los emisores de los mismos una tensión de 0 volt. o casi 5 volt según la

Los condensadores C1, C2, C3 y C4 en un primer momento son un cortocircuito y la tensión aparece casi instantaneamente en la salida, y esta misma tensión sirve para activar y saturar o bien los transistores Q3, Q5 (salida 5v) ó Q4, Q6 (salida 12v).

Los diodos D1 a D4 sirven o para asegurar el corte de los transistores o su saturación.

Los diodos D5 y D6 protegen a los transistores Q5, Q6 respectivamente y se alternan en el estado de no conducción.

La unión de las bases de los complementarios Q5 y Q6 asegura también que mientras uno conduzca (saturación) el otro no lo haga (corte). Así si Q5 conduce en la salida aparecerán los 5v menos VCEQ5 (sat). Si lo hace Q6 se tendrá -12v menos VCEQ6 (sat), este último negativo.

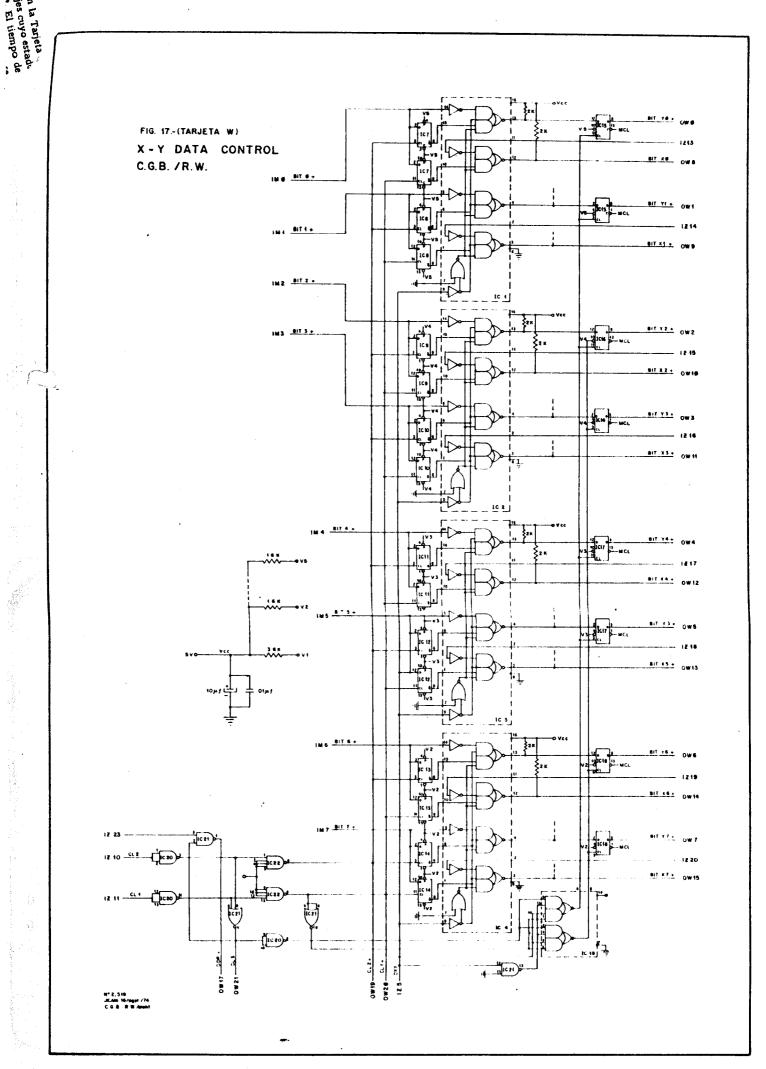

#### 324 Control de Finje de Luice

Tarjeta construída con técnicas de wire wrap, tiene multiples funciones y proporciona las entradas a los conversores digital-analogo. (Fig. 17).

Las entradas CL1 y CL2 reciben las dos fases de reloj provementes del Controlador (3-3.5), se invierten en IC20 por razones de sincronismo en la carga y recirculación de datos. En el proyecto original no existían estos gates, y el resultado fué que en la pantalla sparecían en cuadratura las figuras durante la carga de nuevos datos, specto de las que lo hacían durante la recirculación.

Los gates de IC22 pueden soportar hasta 30 cargas TTL, lo que permite manejar adecuadamente los relojes de los FFs (IC7 a IC14).

La señal CLS es la suma de las dos fases y es utilizada en la Tarjeta del Controlador general (3-3.5).

ODR+ es importante y a través nuevamente del Controlador sirve para avisar al Canal de la aceptación de un dato según lo requerido por la Interfase de la Datacraft. (Out put Data Received).

El resto de la tarjeta es un bloque repetitivo por cada bit de datos, cuya operación es como sique:

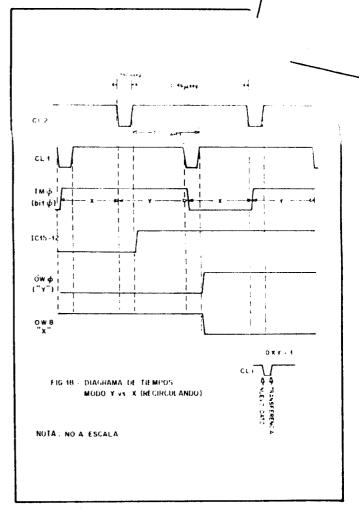

Por cada entrada procedente de la MDR (supongamos el bit  $\phi$ ) se tienen dos salidas (OW $\phi$  y OW8) que corresponden a un dato de coordenadas Y y X respectivamente. Así dos números consecutivos en el tiempo son aparejados y colocados simultaneamente en los conversores digital-análogo representando un punto a graficarse. También se provee la lógica para un gráfico Y vs Barrido Interno.

Asumamos que la señal DXY está "alto" (1 lógico) y aparece un pulso en la fase CL2 del Reloj. La transición positiva de este pulso dispara el primer FF de IC7 que deja pasar el bit  $\phi$  que en este momento corresponde a un dato Y. A su vez el multiplexer IC1 deja pasar este dato que ahora, está ubicado a la entrada D del primer FF de IC15 (IC15-12).

Al presentarse un pulso en CL1 (Fig. 18) la transición positiva, dispara el segundo FF de IC7, nuevamente se produce la transferencia de un dato (esta vez X) del bit  $\phi$  a través del FF y el multiplexer IC1 a la salida OW8. Pero simultaneamente el mismo pulso de Reloj cruzando los gates de IC19 disparan los FFs de IC15 que transfieren el dato Y a la salida OW $\phi$ .

Salvo la diferencia en tiempos de propagación de los diferentes gates, estos datos Y y X aparecen simultaneamente.

La transición negativa de los pulsos de Reloj según lo explicado en 3-3.2 y la Fig. 15, prepara los datos provenientes de la MDR sean Y ó X y la transición positiva los transfiere. De acuerdo al tiempo de puesta de los FFs se tiene pues una restricción en el ancho de estos pulsos que deben ser mayores que este tiempo sumado al de propagación de los registros de corrimiento y otros gates en acción. El valor escogido resultó ser 180µseg.

Cuando DXY está "bajo" (cero lógico) entonces IC1 dejará pasar directamente y para cualquier fase de Reloj el dato del bit  $\phi$  hacia IC15, este último se disparará en cada dato, obteniéndose en OW $\phi$ una reproducción del tren de datos de la entrada bit  $\phi$ .

En la salida OW8 a su vez se reproducirá la entrada IZ13 que corresponde al bit  $\phi$  del contador generador del barrido interno (véase Fig. 11). En conclusión cuando DXY es cero se tiene el modo Y vs Barrido Interno.

Resulta evidente que en el modo Y-X se tiene una limitación de 512 datos y en el modo Y-Barrido Interno una de 1024 datos por la capacidad de la MDR. Esto se puede obviar utilizando otros modos de operación a explicarse posteriormente donde la limitación la da la memoria de la Computadora y no la MDR.

El esquema explicado se repite en forma similar para el resto de bits que conforman una palabra de 8 bits.

#### 3-3.5 Controlador

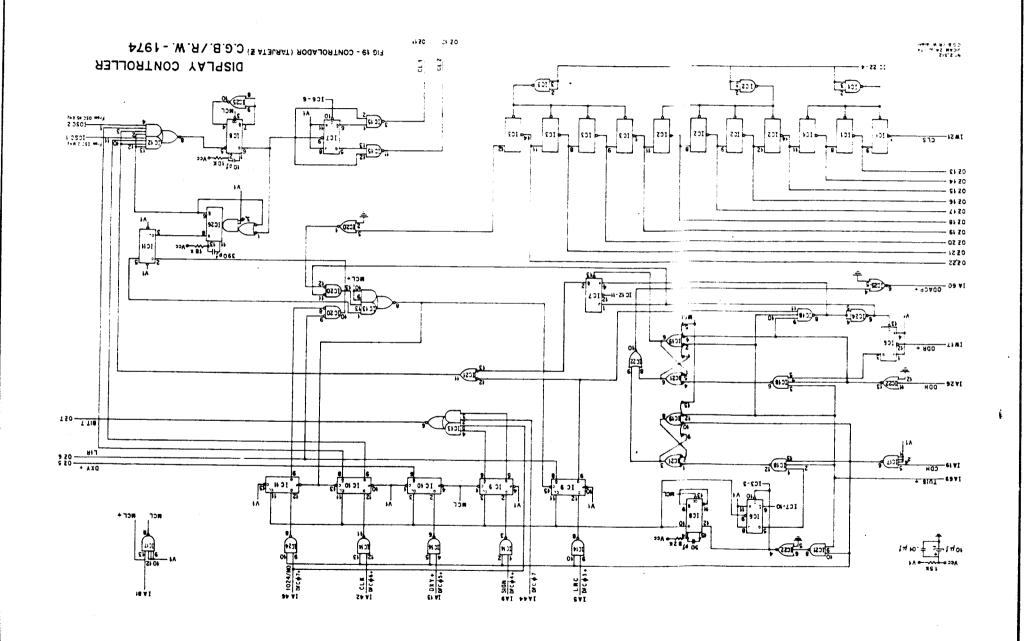

Es la tarjeta más importante, usa wire wrap en su construcción y provee de las señales y comandos adecuados a todas las demás tarjetas, teniendo además que entenderse directamente con el canal de la Computadora e Interfase. El circuito está representado en la Fig. 19.

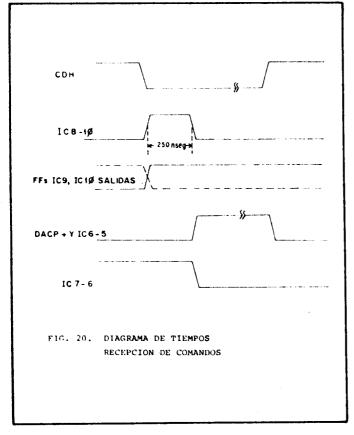

A. Recepción de Comandos:

Se inicia cuando CDH (normalmente en 1) cae a cero. IC17 la invierte; si TUIS+ está en 1 (unidad seleccionada), se libera el FF de IC6 (estaba resetado) y se dispara el monostable IC8 en el ángulo superior izquierdo del diagrama.

El pulso de este monostable tiene un ancho de 250 nseg. y deja

pasar las señales de las líneas de comandos (LRC, SIGN, DXY, CLOCK,1024/NO) que entran a los NAND de IC14 e IC24 y son almacenados en los FFs

IC9, IC10 e IC11. Este mismo pulso invierte la salida del FF IC6 a "alto" (1), señal que es usada por el primer latch (pica porte) formado por gates de IC21 e IC19 para responder me diante la línea DACP+ al canal que el comando ha sido aceptado.

Cuando el canal sensa la respuesta (DACP+) regresa CDH a su nivel normal (alto) con lo que el latch y el FF de ICo se resetean, es decir retoman sus valores normales.

El diagrama de tiempos se muestra en la Fig. 20.

NOTA: DACP+ equivale a ODACP+ (Apéndice).

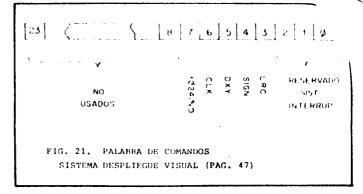

El significado de los comandos es como sigue:

(Load Recirculante). Si está "bajo" indica carga de nuevos LRC datos en oposición a una recirculación (alto).

Con 8 bits por dato se pueden tener dos rangos de trabajo. . SIGN Uno positivo comprendido entre 0-256 (bajo) y el otro ± 127 con negativos en complemento 2 (alto).

Si el gráfico es Y-X ésta señal estará "alto" en oposición a DXY Y-Barrido Interno (bajo).

Se disponen de dos Relojes de 2 MHz y 45 MHz. Este CLK ultimo es apropiado para la recirculación (alto) mientras que el primero para una carga rápida de nuevos datos (ba-10).

1024/NO Si esta linea está "alta" se contará automáticamente el número de datos que ingresan y llegada la cifra de 1024 se producirá una recirculación, así mismo que pasará a trabajar con el Reloj de 45 MHz. Si está "baja", no se producirá ninguna acción especial.

La Figura 21 muestra la palabra de comandos.

Después de ser invertidos y almacenados en los correspondientes FFs, nos valemos de estas señales para decidir acciones o en general guiar el proceso de carga y posterior recirculación de datos de un modo que se explica a continuación.

Recepción de Datos:

Las líneas de datos en (Bit  $\phi$  a Bit 6) se dirigen hacia la MDR salvo el Bit 7 ó de signo que entra a esta tarjeta.

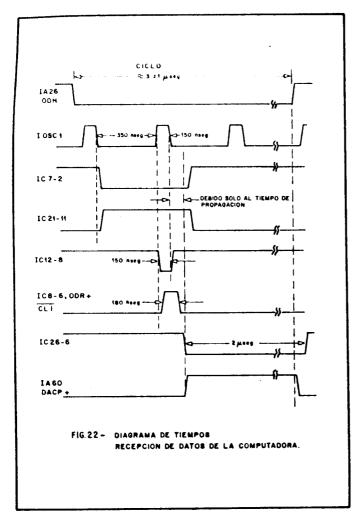

La transferencia de un dato se inicia cuando ODH normalmenpasa a "bajo". Referirse a la Fig. 22 para los siguientes párrafos.

Para esto, antes tiene que haberse recibido los comandos apro-

piados que preparen la transferencia. Así la recepción de un comando implica inicializar el contador formado por IC1, IC2 e IC3 a cero, también clarificar el FF de IC7 en la parte inferior derecha (Fig. 20). Esto último se hace para que la carga de datos se inicie con CL1 a manera de sincronización, así posteriormente y sin errores podremos distinguir un dato Y de un X.

El comando recibido por IA42 selecciona el reloj de 2 MHz para una carga rápida de datos. La señal ODH es comparada en IC18 (salida 8) con TUIS+ (unidad seleccionada) y con el comando de carga (IC9-9 en 1 para carga). Si la orden es de carga y hay un dato esperando, las entradas J y K del FF de IC7 (patas 1 y 4) toman los valores 1 y 0 respectivamente. El reloj de este FF es IOSC1 ó sea 2 MHz y con la primera transición negativa IC7-2 (Q) pasará de 1 a 0 con lo que IC21-11 permite el acceso del reloj a IC8 a través de IC12. Referirse a la Fig. 22 para el diagrama de tiempos.

La aparición de un pulso de Reloj (transición negativa) a la salida de IC12 dispara a IC8, monostable con un ancho de pulso de 180 nseg. El pulso del monostable se transmitirá invertido, alternativamente a las salidas CL1 y CL2 generando las dos fases de Reloj usadas en otras tarjetas (Fig. 15).

La transición negativa del pulso en IC8-6 dispara a su vez a 1C26, otro monostable con un ancho de 2 µseg, que inhibe durante este tiempo el paso del reloj hacia IC8, permitiendo se complete totalmente el ciclo de la transferencia.

La fase de reloj sea que salga por CL1 ó CL2 va hacia la tarjeta del Adaptador de Reloj y Control de Flujo; precisamente en esta última se genera ODR (Output Data Received) señal que en su transisción negativa invierte a IC6-3 (normalmente en cero) y a través del segundo latch produce la respuesta DACP+a la computadora acerca de la aceptación del dato. Este mismo latch retorna a 1 a IC7-2 clarificado el FF con lo cual queda inhibido también el pase de IOSC1 a IC8 hasta un nuevo ciclo (Latch formado por IC21, IC19).

El ciclo se completa cuando el canal retorna ODH a la normalidad, con lo que el latch (DACP+) y IC6-3 retoman sus valores

La Fig. 22 debe suplir cualquier deficiencia en la explicación de la secuencia de recepción de datos.

Contador:

Formado por IC1 a IC3, recibe los pulsos sea de CL1 ó CL2 y los cuenta hasta llegar a 1024 partiendo de la inicialización en cero después de la recepción de un comando. Sus salidas pasan a la tarjeta de Control de flujo de salida (vease pag. 23 y Fig. 11) para la generación de barrido.

Cuando existe la condición de carga y el comando 1024/NO fue puesto, la cuenta de datos recepcionados partiendo de cero se lleva a cabo con este contador. Al arribar al número 1023 (todos los FFs de IC1 a IC3 con salida 1 excepto el que esta más a la derecha), se preparan las condiciones para que recibido el próximo pulso de reloj automaticamente se reinicie la recirculación. Así con la transición negativa en IW21 (CLS) y transcurrido un tiempo de propagación (el de 10 FFs) el último FF pasa de cero a uno con lo que IC13-8 efectúa una transición opuesta (uno a cero) clarificando IC9-9, IC10-9 y preseteando IC11-9. Esto equivale a un comando de recirculación, reloj de 45 Khz y resetear el comando 1024/NO.

Con el siguiente pulso de reloj (primero de recirculación) IC11-5 pasa de 1 a 0 e IC13-8 regresa a 1 con lo que las condiciones de recirculación se hacen permanentes.

Si 1024/NO no hubiera estado puesto; IC13-8 siempre se mantiene en 1 no produciendo ningún efecto especial.

D.

Según el estado de IC9-5 se indicará el rango de los números a mostrarse en el Display esto es 0°256 ó±127 en complemento 2 para los negativos.

En el primer caso dejamos pasar el bit 7 con su valor, esto es IC13-2 se conecta a bit 7 (IA44) y la salida 0z7 será simplemente bit 7.

En el segundo caso, 0z7 será bit 7 por lo que IC13-5 se conecta a bit 7 (IA46).

En el rango 0-256 no debe haber dificultad en comprender el porqué del procedimiento seguido. Para ±127 si puede requerirse dar mas detalles refiriéndonos a la Tabla 2.

En la primera columna está el número decimal, en la segunda su representación binaria en 2' y en la tercera igual a la segunda pero con el bit 7 de signo complementado.

Claramente se ve que si los bits de la columna 2 entraran a un DAC, éste tomaria a los negativos como que fueran mayores y en consecuencia la tensión análoga de salida no estaria de acuerdo con la magnitud real de los números. En cambio si los bits de entrada al DAC fueran los de la columna 3, salvo un bias general el orden de magnitud sería el adecuado correspondiendo una salida análoga de 0 volt. a -127 y el máximo (10 volt) a +127.

Lo que se ha hecho en realidad es sumar un "bias" a todos los números.

Binario en 2' Binario (bit 7)

| Binario en 2' |    |    |    |    |    |    | Binario (bit /) |    |    |    |    |    |            |    |    |    |

|---------------|----|----|----|----|----|----|-----------------|----|----|----|----|----|------------|----|----|----|

| Número        | В7 | В6 | В5 | В4 | в3 | B2 | <b>B</b> 1      | вø | В7 | В6 | В5 | B4 | <b>B</b> 3 | В2 | В1 | вр |

| - 127         | 1  | 0  | 0  | 0  | 0  | 0  | 0               | 0  | 0  | 0  | 0  | 0  | 0          | 0  | 0  | 0  |

|               | .  | •  |    |    | •  |    |                 |    |    | •  |    | •  | •          | •  | •  | •  |

|               | ١. | ,  |    |    |    |    |                 | •  | .  | •  | •  | •  | •          | •  | •  | ٠  |

| - 1           | 1  | 1  | 1  | 1  | 1  | 1  | 1               | 1  | 0  | 1  | 1  | 1  | 1          | 1  | 1  | 1  |

| 0             | 0  | 0  | 0  | 0  | 0  | 0  | 0               | 0  | 1  | 0  | 0  | 0  | 0          | 0  | 0  | 0  |

| + 1           | ٥  | 0  | 0  | ٥  | 0  | 0  | 0               | 1  | 1  | 0  | 0  | 0  | 0          | 0  | 0  | 1  |

| .             |    | •  | •  | •  | •  |    | •               | •  | •  | •  | •  | •  | •          | ٠  | •  | •  |

| 1 .           |    | •  |    |    | •  | •  |                 | •  |    | •  | •  | •  | •          | •  | •  | ٠  |

| +127          | 0  | 1  | 1  | 1  | 1  | 1  | 1               | 1  | 1  | 1  | 1  | 1  | 1          | 1  | 1  | 1  |

#### 3-3.6 Conversores Digital-Análogo

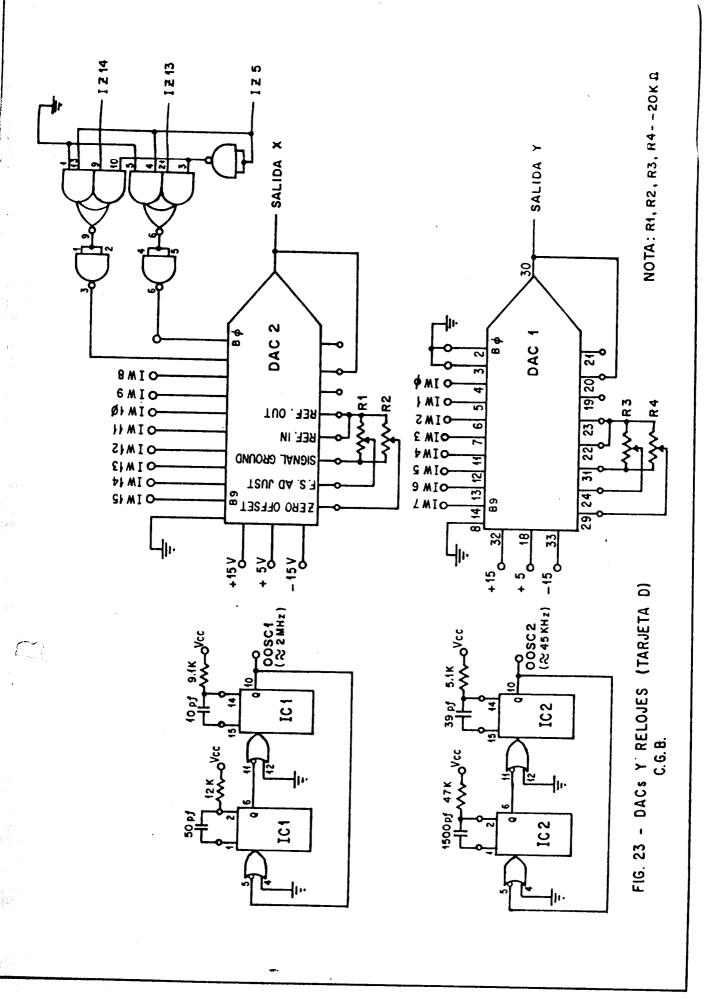

En la Fig. 23 se encuentra el esquema de esta tarjeta donde se han montado dos circuitos DAC híbridos, modelos CY2135 de 10 bits y fabricados por CYCON Inc.

Como todo DAC se tienen las entradas binarias y la salida análoga. Se observa a su vez controles de ajuste de 0 volt. y escala máxima (full scale) y alimentación DC que en este caso es de +15, -15 y 5 volt.

En esta misma tarjeta van montados los dos Relojes (45 KHz y 2 MHz) implementados a través de dos monostables realimentados (astables). La frecuencia se ajusta variando resistencias y condensadores según especificaciones del fabricante.

#### 3-4 Programas de Control y Prueba

Se han implementado varias rutinas, unas estrictamente de control y otras para pruebas o diagnósticos del Sistema.

#### 3-4.1. Rutinas de Control

Son las principales y por ende indispensables en el uso del Display.

Se dispone de 4 rutinas separadas en dos bloques: Display XY o Y: En este caso se deben definir dos arreglos enteros de dimensiones 512 cada uno (o uno de dimensión (1024) que contengan los datos X-Y (o Y solamente).

Si se necesita graficar datos con control de ambas coordenadas (X-Y), el llamado será:

CALL DISPLY (\$\phi\$ IRANK, IY, IX, NUM).

Si el gráfico es Y vs. barrido generado internamente:

CALL DISPLY (1, IRANK, IY, NUM).

donde:

$IRANK = \begin{cases} \phi \text{ para números IX, IY entre } \phi \text{ a 255} \\ 16 \text{ "IX, IY "-127a + 127} \end{cases}$

IX, IY arregios enteros de datos

NUM = número de puntos por graficarse con un máximo de 512 en X-Y y 1024 para Y solo.

NOTA: Los puntos no especificados son llenados con ceros y automaticamente se inicia una recirculación de los datos en la pantalla.

DAC X-Y o Y: En este caso se hace el gráfico punto por punto y por lo tanto no es necesario definir arreglos; sino que cada vez que se disponga de un nuevo dato se llama a la rutina apropiada.

Se usan dos rutinas: la primera que podría decirse de inicialización y la segunda la de los datos propiamente dicha.

CASO X, Y: Secuencia de llamado CALL DAC (φ, IRANK)

una vez al comienzo y:

CALL DDATA (IY, IX)

por cada dato

CASO Y:

CALL DAC (1, IRANK)

una vez al comienzo

CALL DDATA (IY)

por cada dato

El tiempo máximo admisible entre dato y dato es de aproximadamente 2 mseg (unas 1000 instrucciones de Assembly, 80 Fortran). Si se sobrepasa este límite los puntos no quedarán grabados en la memoria recirculante dinámica y habrá errores en una posterior recirculación

Nótese que ahora no hay limitación en cuanto al número de puntos de graficarse, en todo caso estos están dados por la memoria de la Computadora.

Recirculación: Para ser usado con el caso DAC X-Y o Y: de este modo, en cualquier momento se ordena la recirculación de los últimos datos (512 en X-Y o 1024 en Y).

#### CALL REC

El listado de estas rutinas implementadas en lenguaje Assem bler aparece en las próximas páginas.

#### 3-4.2 Rutinas de Prueba

Se han confeccionado varias, sin embargo la principal es la nominada "Diagnostic Test", cuyo listado está en páginas posteriores. (Hecho usando FORTRAN IV).

Basicamente este programa prueba los cuatro modos descritos en 3-4.1 aprovechando de los llamados "sense switches" en la consola de la DC6024/3 y de acuerdo a la siguiente Tabla

| 1          | * DISPLAY SOFTWARE CONTROLLER         |            |              |                                       |  |  |

|------------|---------------------------------------|------------|--------------|---------------------------------------|--|--|

| 2          | * FIRST VERSION CGB MAY/74            |            |              |                                       |  |  |

| 3          | * CALLING MODE. SEE INSTRUCTION SHEET |            |              |                                       |  |  |

| 4          | *                                     |            |              |                                       |  |  |

| 5          | * DISPLAY                             | MODE       |              |                                       |  |  |

| 6          | •                                     |            |              |                                       |  |  |

| 7          | *                                     |            |              |                                       |  |  |

| 8          | •                                     | XEQV       | XYDU, '0410  |                                       |  |  |

| 9          | 210                                   | XDEF       | DISPLAY, DIS |                                       |  |  |

| 10<br>11   | DIS                                   | GAP        | 1            | . BRING MODE ADDRESS                  |  |  |

| 12         |                                       | TMK        | φ,1          | . MODE NUMBER ?                       |  |  |

| 13         |                                       | GAP        | 1            |                                       |  |  |

| 14         |                                       | TME        | φ,1          | . SIGN                                |  |  |

| 15         |                                       | SOK        | 1            | . IS MODE -φ?                         |  |  |

| 16         | MODXY                                 | BOZ        | MODY         | NO, THEN DISPLAY Y                    |  |  |

| 17         | MODAI                                 | GAP        |              | YES, THEN DISPLAY XY                  |  |  |

| 18         |                                       | TMK*       | ],J          | OF PAIRS OF DATA                      |  |  |

| 19         |                                       | TOA<br>AEA | '24 φ        | . XY COMMAND                          |  |  |

| 20         |                                       | OCM        | #XYDU        | . SIGN COMMAND                        |  |  |

| 21         |                                       | BNZ        | *.1          |                                       |  |  |

| 22         |                                       | TME        | φ,j          |                                       |  |  |

| 23         |                                       | AKI        | Ψ,σ          |                                       |  |  |

| 24         |                                       | AKE        |              |                                       |  |  |

| 25         |                                       | AIM        | TX           | . X ADDRESS TO APPROPIATE INST.       |  |  |

| 26         |                                       | AEM        | TY           | . Y ADDRESS                           |  |  |

| 27         |                                       | TNI        | 1025         | · · ADDRESS                           |  |  |

| 28         |                                       | AKI        |              |                                       |  |  |

| 29         |                                       | AKI        |              | . I = UNFILLED PLACES                 |  |  |

| 30         |                                       | NKK        |              | · · · · · · · · · · · · · · · · · · · |  |  |

| 31         | TX                                    | TMA        | φ.K          |                                       |  |  |

| 32         |                                       | ODW        | #XYDU        | . X DATA TO REGISTER A                |  |  |

| 33         |                                       | BNZ        | <b>*-1</b>   |                                       |  |  |

| 34         | TY                                    | TMA        | φ,κ          |                                       |  |  |

| 35         |                                       | ODW        | #XYDU        | . Y DATA TO REGISTER A                |  |  |

| 36         |                                       | BNZ        | *-1          |                                       |  |  |

| 37         |                                       | BWK        | TX           |                                       |  |  |

| 38         | TZA                                   | TZA        |              |                                       |  |  |

| 39         | ZERO                                  | BWI        | LOOP         |                                       |  |  |

| 40         | RETURN                                | TMI        | тамфк        |                                       |  |  |

| 41         |                                       | TIM        | TX           |                                       |  |  |

| 42         |                                       | TIM        | TY           | . INITILIZE FOR NEXT CALLING          |  |  |

| 43         |                                       | TIM        | TYY          |                                       |  |  |

| 44         | 1.000                                 | BUC        | 2,J          | RETURN                                |  |  |

| 45         | LOOP                                  | ODW        | #XYDU        | . FILL WITH ZERO                      |  |  |

| 46<br>47 ° |                                       | BNZ        | *.}          |                                       |  |  |

| 48         | MODY                                  | BUC        | ZERO         | 22002 4 4222                          |  |  |

| 49         | MODT                                  | GAP        | 1.           | . BRING X ADDRESS                     |  |  |

| 50         |                                       | TMK*       | φ.1          | . #OF DAT                             |  |  |

| 51         |                                       | TOA<br>AEA | '200         | . COMMAND WORD                        |  |  |

| 52         |                                       | OCW        | *XYDU        | . SIGN                                |  |  |

| 53         |                                       | BNZ        | *.1          |                                       |  |  |

| 54         |                                       | AKI        | 1            |                                       |  |  |

| 55         |                                       | AIM        | TYY          | INITE ALUE THE AUCTOLOGICAL           |  |  |

| 56         |                                       | TNI        |              | . Initialize tma instruction          |  |  |

| 57         |                                       | AKI        | 1φ25         |                                       |  |  |

| 58         |                                       | NKK        |              | LOOP INDEVE                           |  |  |

| 59         | TTY                                   | TMA        | ø.ĸ          | . LOOP INDEXES                        |  |  |

| 60         | •••                                   | ODW        | ΨXYDU        | . OUTPUT Y DATA                       |  |  |

| 61         |                                       | BNZ        | *·1          | . COITOI I DAIA                       |  |  |

| 62         |                                       | BWK        | TYY          |                                       |  |  |

| 63         |                                       | SOJ        | 1            |                                       |  |  |

| 64         |                                       | BUC        | TZA          |                                       |  |  |

| 65         | TMAØK                                 | DATA       | 'φ53φφφφφ    |                                       |  |  |

|            |                                       |            |              |                                       |  |  |

| 2  | * DAC M | ODE AND | RECIRCULATI  | ON                                    |

|----|---------|---------|--------------|---------------------------------------|

| 3  |         |         |              | 014                                   |

| 4  | •       |         |              |                                       |

| 5  |         | XDEF    | DAC, DAC     |                                       |

| 6  |         | XDEF    | DDATA, DD    | 0.00                                  |

| 7  |         | XDEF    | REC. REC     | N I N                                 |

| 8  | DAC     | GAP     | l LEG, REC   |                                       |

| 9  |         | TMK     | i, ن<br>ن, ن |                                       |

| 10 |         | GAP     | 1            | . BRING MODE NUMBER                   |

| 11 |         | TME     | φ,ι          | . +OR, + AND - NUMBERS                |

| 12 |         | TEM     |              |                                       |

| 13 |         | TKM     | SP           | SIGN POINTER                          |

| 14 |         |         | DMF .        | . SFT DISPLAY MORE FLAG TO DACKY      |

| 15 | MODø    | CZK     |              |                                       |

| 16 | морф    | BNZ     | MODI         | MODE NUMBER?                          |

| 17 |         | TOA     | 'Φ4φ         | . COMMAND WORD                        |

| 18 |         | AEA     |              | PLUS SIGN COMMAND                     |

|    |         | OCW     | #XYDU        |                                       |

| 9  |         | BNZ     | *-1          | . INSIST IF BUSY                      |

| 20 | MODI    | TOA     | 'φφφ         | . COMMAND WORD                        |

| 21 |         | BUC     | įίφ          | RETURN                                |

| 22 |         | AEA     |              | . SIGN                                |

| 23 |         | OCM     | #XYDU        |                                       |

| 4  |         | BNZ     | *-I          |                                       |

| :5 |         | BUC     | φ.j          | RETURN                                |

| 6  | DDATA   | CZM     | DMF          | . XY OR Y MODE                        |

| 7  |         | BNZ     | YDATA        | · · · · · · · · · · · · · · · · · · · |

| 8  | XDATA   | GAP     | 1            | . I (X) ,J (Y)                        |

| 9  |         | TMA     | ø.1          | . DISPLAY X                           |

| 0  |         | ODW     | #XYDU        | . DISTERT X                           |

| 1  |         | BNZ     | *-1          |                                       |

| 2  | YDATA   | TMA*    | ø,J          |                                       |

| 3  |         | ODW     | XYDU         | . DISPLAY Y                           |

| 4  |         | BNZ     | *.1          | . DISPLAT Y                           |

| 5  |         | BUC     | آبر ا        |                                       |

| 6  | REC     | TMK     | DMF          | ACKING TO THE TOTAL TOTAL             |

| 7  |         | BOZ     | XY           | ASKING FOR XY OR Y                    |

| 8  | Y       | TOA     | 110          | DMF- THEN SKIP TO XY                  |

| 9  | RCW     | TME     | SP SP        | NO, THEN Y COMMAND                    |

| 0  |         | AEA     | J.F          | . SIGN POINTER                        |

| ı  |         | OCW     | #XYDU        |                                       |

| 2  |         | BNZ     | *.1          |                                       |

| 3  |         | BUC     | φ,3          | Demins                                |

| 4  | XY      | TOA     | Ψ,3<br>'15 Φ | RETURN                                |

| 5  |         | BUC     | RCW          | . XY COMMAND                          |

| 5  | DMF     | DATA    |              |                                       |

| ,  | SP      | DATA    | φ<br>φ       |                                       |

| 3  | ٠.      | END     | Ψ            |                                       |

| -  |         | END     |              |                                       |

# FRESA

FABRICACIONES REPARACIONES ELECTRICAS S.A.

#### **REBOBINADO**

MOTORES

ALTERNADORES

TRANSFORMADORES

MAQUINAS DE SOLDAR

#### **FABRICACIONES**

- TRANSFORMADORES DE POTENCIA Y MEDIDA

SECCIONADORES UNIPOLARES

- JORGE CHAVEZ 162 BRENA Tel. 310390 - 310461

END

Tabla II

| Modo     | Switch 1 | Switch 2 | Switch 3 | Switch 4 |

|----------|----------|----------|----------|----------|

| AUSA     | OFF      | OFF      | OFF      | ON       |

| isplay Y | OFF      | OFF      | OFF      | OFF      |

| splay XY | ON       | OFF      | OFF      | OFF      |

| AC XY    | OFF      | ON       | OFF      | OFF      |

| AC Y     | OFF      | OFF      | ON       | OFF      |

a figuras generadas en la pantalla son como en la Fig. 24.

DIAGNOSTIC TEST (FORTRAN IV) MODO XY USA UNA ESPIRAL MODO Y USA UN SINUSOIDE DIMENSION IX (1024), IY (1024) INTEGER X, Y, XYFLAG, YFLAG, S DATA NX, PL/100 3.14159265/ DELT:(2.0\*PI)/1024. DELP-(2\*PI)/8. 0 DELXY  $(2.\phi * PI)/512$ . XYFLAG . Ø YFLAG . Ø PAUSE SETSW CALL SSWITCH (1,S) IF (S.EQ.1)GO TO 6Φ CALL SSWTCH (2,S) IF (S.EQ.2) GO TO 2 XYFLAG:1 GO TO 6 Ø CALL SSWTCH (3,S) IF (S.EQ.2)GO TO 18 YFLAG.I PHASE . ØØ PHI.  $\phi \phi$ DO 301 . 1,1024 IY(I) - 127.\*SIN (PHI+PHASE) PHI . PHI-DELT IF (YFLAG. EQ.1) GO TO 4  $\phi$

PHASE-PHASE + DELP

(a) (b)

Fig.24 IMAGENES DE PRUEBA

Estas permanecen fijas en la alternativa "DAC" y se mueven según las flechas en "DISPLAY".

#### 3-5 Montaje de Tarjetas y Equipo

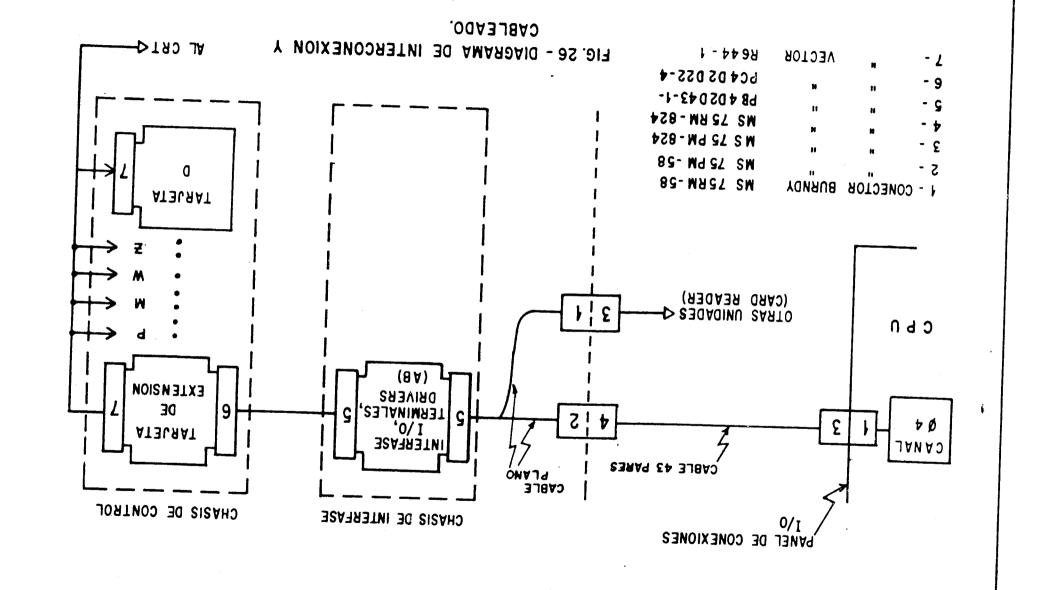

Se dispone de un osciloscopio (CRT) usado como pantalla, un chasis de Interfase y otro de Control. En el de Interfase se ha colocado la tarjeta AB (véase TABLA I, Pag. 29), mientras que en el chasis de control van el resto de tarjetas (M, C, W, Z, D).

Un diagrama de interconexiones bastante explicativo de por sí es el de la Fig. 9.

El diagrama de cableado está en la Fig. 26, ahí se indican los tipos de cable usados, conectores o sockets.

# FABEM

MATERIALES ELECTRICOS Y MECANICOS S.A.

- TRANSFORMADORES DE POTENCIA

- TRANSFORMADORES DE MEDIDA

- CELDAS DE ALTA TENSION

- TABLEROS DE MANDO

- MAQUINAS DE SOLDAR

- RECTIFICADORI 5 PARA GALVANOPLASTIA Y TRACCION

OMICRON 555

PARQUE INTERNACIONAL DE INDUSTRIA Y COMERCIO — CALLAO

TELEFONO: 51-5766 — APARTADO 2891 — LIMA 1

#### 4 - CASOS PRACTICOS DE APLICACION

Los usos de este periférico, son muy variados como es facil suponer. Se le utiliza en el monitoreo de señales generadas en la computadora o que estaban grabadas digitalmente, para observar correlaciones, espectros de potencia, gráficos variables en el tiempo, etc. Como ejemplo véase la Fig. 29.

#### 4.1 Simulación de Voz

En Jicamarca se dispone de un ADC, de modo que es fácil digitalizar voz, simular por ejemplo las distorsiones que sufriría esta, al atravesar un supuesto medio de comunicaciones (caso de un sistema que usa el Electrochorro Ecuatorial), en fin incluir efectos de dispersión atmosferica, distorsión de equipo y otros, para finalmente la voz digitalizada pasarla por el DAC diseñado, amplificarla, filtrarla y escuchar el resultado final para su estudio.

Este es un caso típico donde intervendría el tema de éste tra-

a) 4 canales de Infrasonido

b) Generación de números

FIG. 29. APLICACIONES

#### Conclusiones

El Sistema Digital diseñado permite disponer de un Conversor Digital-Análogico para uso con la Computadora DC6024/3. La circui-

tería integrada que se ha empleado, brinda además un cos... y alta confiabilidad.

El fin inmediato que se persigue es el de visualización  $2k_{\rm co}$  almacenados digitalmente en la Computadora, aunque esto no resulta ge los múltiples usos propios de un DAC genérico.

Los campos de aplicaciones son númerosos y variados y arginos ya se mencionaron, en fin se dispone ahora de una herramienta útil y que puede ser aprovechada en diversidad de formas.

#### Agradecimiento

En las etapas de diseño y prueba participaron reconocidamente el Ing. Carlos Urquizo, Srta. Carmen Clavo y Sr. Juan Nizama.

Se agradece también a los Ings. Manuel Chavez y César La Hoz por sus sugerencias, el Ing. Cesar Valladares quien proporciono datos para el Capítulo 4 es igualmente reconocido.

Los dibujos y esquemas son del Sr. Armin Hoempler, las fotos del Sr. Jaime García y el mecanografiado de la Srta. Gladys Pardo F., a todos ellos expreso mi agradecimiento.

Finalmente, es justo reconocer la colaboración de todo el personal del ROJ, su participación y ayuda posibilitó la conclusión del Proyecto.

#### BIBLIOGRAFIA

- Datacraft Corporation, Fort Lauderdale, Florida. "Reference Manual DC6024/1 and DC6024/3 Computer Systems". 1972

- . ---- "Input-Output Interface Reference Manual". 1970

- 5. \_\_\_\_ "Technical Write-up Interfacing to Data craft Series 6024 Computers". 1970

- IEEE Spectrum. "Computer Report VI. Minicomputer Interfaces: Know More, Save More". IEEE Spectrum, 11, 65-68, Febrero 1974.

- Intel Corporation, Mountain View, California. /"Catalogue" 1970/.

- Signetics Corporation, Sunnyvale, California. "Signetics Digital 54/7400 Data Book". /1972/.

- Peatman, J.B. "The Design of Digital Systems". New York, McGraw-Hill Book Co. 1972.

- Texas Instruments Incorporated. "Designing with TTL Integrated Circuits", New York, McGraw-Hill Book Co. /1970/

### CE-YE-SA

#### **INGENIERIA ELECTRICA**

- \* FABRICACION DE TABLEROS ELEC-TRICOS.

- \* FABRICACION DE SUB-ESTACIONES DE TRANSFORMACION.

- \* PROYECTOS E INSTALACIONES ELEC-TRICAS INDUSTRIALES.

- \* EQUIPOS ELECTRICOS DE CONTROL.

Parque Internacional de Industria y Comercio Lima - Callao

OMEGA Nº. 225 — AVENIDA COLONIAL CUADRA 57 — TELFS.: 51-0617 — 51-5345

#### APENDICE A

#### NOMENCLATURA EN DIAGRAMAS

Tarjeta AB 6 de Interfase.- Referirse a la página 15 para una explicación detallada.

Resto de tarjetas o Diagramas. -- A cada tarjeta construída se le ha asignado un código identificatorio (Tabla I, página 15).

Si la señal es una entrada, en el diagrama se le reconoce por la letra "I" inicial. Ejemplo en el diagrama de la MDR (tarjeta "W" y Fig. 14 se encuentra:

Esto significa entrada proveniente de la tarjeta "Z" y que puede localizarse en el correspondiente diagrama (Fig. 19) como OZ 13. Si la señal es de salida su código empieza con una "O", así:

significa salida de la tarjeta "W" número  $\phi$

Las señales sean de entrada o salida se distribuyen en los contactos de las tarjetas implementadas de acuerdo a las Tablas III a, b, c, d, e

Véase la página 15 para otros detalles.

#### APENDICE B

#### ABREVIATURAS MNEMOMICAS

| ABC       | Automatic Block Controller            |

|-----------|---------------------------------------|

| ADC       | Analog to Digital Converter           |

| CDH       | Command Data Here                     |

| CLS       | Clocks (Relojes)                      |

| CLK       | Clock (Reloj)                         |

| CNCT      | Connected                             |

| CPU       | Central Procescing Unit               |

| CRT       | Cathode Ray Tube                      |

| DAC       | Digital to Analog Converter           |

| DATU      | Data Accepted to Unit                 |

| DAVFU     | Data Available from Unit              |

| DC6024/3  | Datacraft Computer modelo 6024/3      |

| DFU       | Data from Unit                        |

| DISC      | Disconnect                            |

| DPY       | Display                               |

| DXY       | Display modo XY                       |

| DTU       | Data to Unit                          |

| ECBI      | Enable Channel Buffer Empty Interrupt |

| IC        | Integrated Circuit                    |

| IIFU      | Input Interrupt from Unit             |

| IDW       | Input Data Word                       |

| ISW       | Input Status Word                     |

| I/O       | Input/Output ·                        |

| LRC       | Load - Recirculate                    |

| MCL       | Master Clear                          |

| MDR       | Memoria Dinámica Recirculante         |

| OCW       | Output Command Word                   |

| ODACP     | Output Data Accepted                  |